# Comparison of Microwave Inductors Fabricated on Silicon-on-Sapphire and Bulk Silicon

R. A. Johnson, *Student Member, IEEE*, C. E. Chang, *Member, IEEE*, P. M. Asbeck, *Member, IEEE*, M. E. Wood, G. A. Garcia, and I. Lagnado, *Member, IEEE*

**Abstract**— Inductors are important elements of microwave circuits that frequently require high self-resonant frequencies and high quality factors. In this work, circular spiral inductors fabricated on silicon-on-sapphire (SOS) and bulk silicon are compared. Due to the low-loss dielectric substrate, SOS inductors showed both higher self-resonant frequencies and higher quality factors than those fabricated on bulk silicon. Small-signal models extracted for the inductors confirm that the degradation of the inductor characteristics in bulk silicon stems from losses in the substrate.

## I. INTRODUCTION

IMPROVEMENTS in silicon device performance combined with low cost are making silicon an increasingly attractive technology for high-frequency radio frequency (rf) and microwave personal communication circuits. Silicon-on-sapphire (SOS) technology provides a variety of advantages over bulk silicon such as reduced parasitic capacitance, simplified processing, elimination of backgating, and radiation hardness. Recently, SOS MOSFET's have shown  $f_t$  values above 20 GHz and  $f_{max}$  values above 60 GHz for both n- and p-channel devices [1], [2]. In order to realize silicon circuits in the microwave regime, however, passive elements such as inductors and capacitors are needed. In this letter, we show that the high dielectric quality of the SOS substrate ( $\epsilon_r = 9.39$ ,  $\tan \delta < 0.0001$  at 3 GHz,  $\rho = 10^{14} \Omega\text{-cm}$ ) permits realization of higher-performance inductors than those fabricated in bulk silicon.

Many novel processing techniques such as deep trench etches under the inductor [3], [4] and thick gold metallization [5], [6] have recently been investigated in order to improve inductor performance with bulk silicon. Our inductors use a standard digital CMOS process with aluminum metallization and rely only on the sapphire substrate to improve their performance. This eliminates the need to develop costly and less reliable process steps.

Manuscript received March 13, 1996. This work was supported by the Independent Research Program and the ONR 6.2 Microelectronics Project at NCCOSC RDTE Division.

R. A. Johnson and P. M. Asbeck are with the Department of Electrical and Computer Engineering, University of California, San Diego, La Jolla, CA 92093-0407 USA.

C. E. Chang was with the University of California, San Diego, CA USA. He is now with Rockwell Science Center, Thousand Oaks, CA 91360 USA.

M. E. Wood, G. A. Garcia, and I. Lagnado are with the Naval, Command, Control, and Ocean Surveillance Center, RDT&E Division (NRaD), San Diego, CA 92152-7633 USA.

Publisher Item Identifier S 1051-8207(96)06516-6.

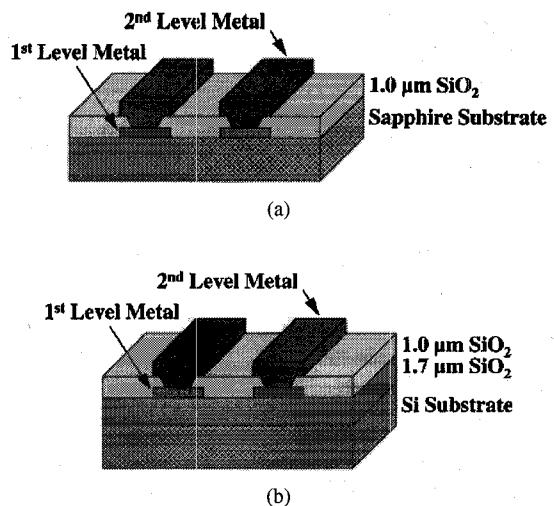

Fig. 1. Cross section of the SOS (a) and bulk silicon (b) inductors.

## II. PROCESSING

Circular spiral inductors with 5  $\mu\text{m}$  metal width and spacing were processed at NRaD's Integrated Circuit Research and Fabrication Branch using a double level metal process optimized for digital applications. The inductors were processed on both SOS and bulk silicon ( $\sim 8\text{--}10 \Omega\text{-cm}$ ). For the latter case, a 1.7- $\mu\text{m}$ -thick  $\text{SiO}_2$  insulating layer was deposited on top of the bulk silicon wafers before fabricating the inductors. Second-level metal (1.6- $\mu\text{m}$  TiW/Al/Ti) was separated from first-level metal (0.5- $\mu\text{m}$  TiW/Al/Ti) by a 1- $\mu\text{m}$  inter-level dielectric of  $\text{SiO}_2$ . Cross sections of the inductors for the different substrates are shown in Fig. 1. In order to reduce parasitic resistance, vias were placed along the length of the spiral, except in the over crossing area. This yielded a thicker effective metallization with an overall sheet resistance of  $\sim 17 \text{ m}\Omega/\text{sq}$ . for the combined metal layers.

## III. INDUCTOR MEASUREMENTS AND RESULTS

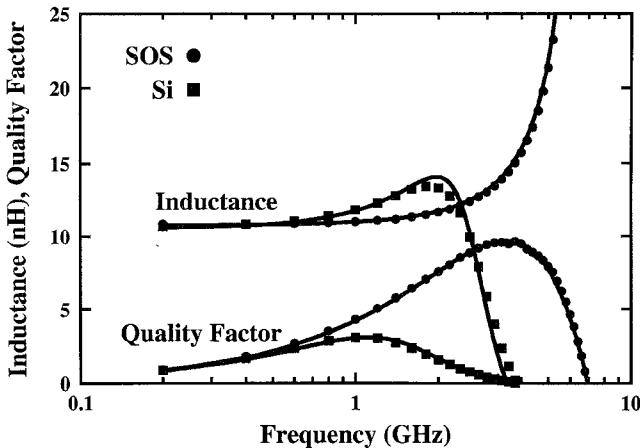

Two-port s-parameter measurements were made using an HP8510B network analyzer from 0.5–20 GHz. Open and short circuit test patterns were probed to measure pad parasitics for de-embedding. The inductance and quality factor for eight-turn inductors fabricated on SOS and on bulk silicon are shown in Fig. 2. The SOS inductor had a higher self-resonant frequency and a three-fold increase in the peak quality factor

Fig. 2. Measured (symbols) and modeled (line) inductance and quality factor for an eight-turn inductor on SOS (●) and bulk silicon (■).

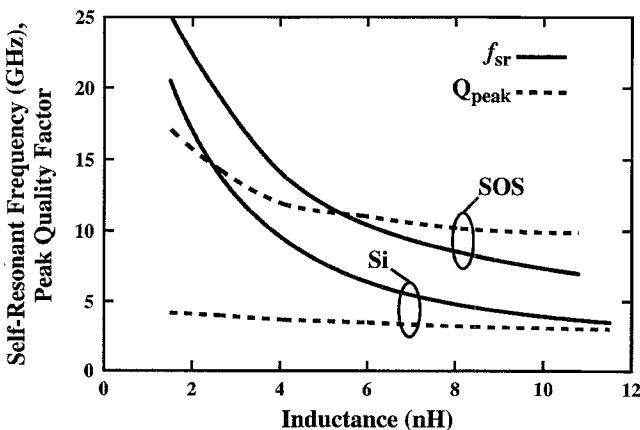

Fig. 3. Self-resonant frequency (line) and peak quality factor (dashes) of inductors on SOS and bulk silicon.

over the bulk silicon inductor. The self-resonant frequency and peak quality factor for various inductors are plotted versus inductance in Fig. 3. The SOS inductors have significantly better performance than the bulk silicon inductors.

It is important to note that at low frequencies the quality factor is limited by the metal resistance of the spiral and the inductors on SOS and Si are comparable. At higher frequencies, however, the  $Q$  is limited by the substrate losses and the SOS inductors have a distinct performance advantage. To achieve a higher  $Q$ , additional metallization layers can be added or a lower resistance metal such as gold can be used [5], [6].

#### IV. INDUCTOR MODELING

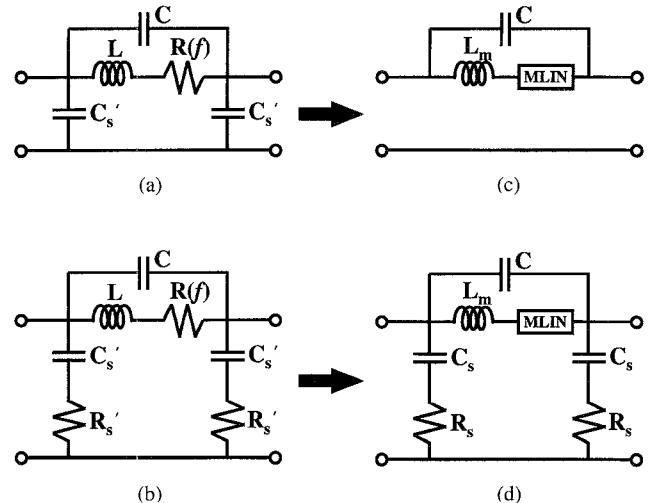

The measured results were fit to a small-signal model using HP/EEsof's microwave circuit simulator LIBRA. Traditional small signal models for inductors on insulating and noninsulating substrates are shown in Fig. 4(a) and (b). For our inductors, the skin effect of the series resistance was important at high frequencies. We took this into account within the LIBRA simulation by using a microstrip line (MLIN) to model the

Fig. 4. Small-signal inductor models. Traditional: (a) insulating substrate and (b) noninsulating substrate. This work: (c) SOS inductors and (d) bulk silicon inductors.

metal trace [Fig. 4(c) and (d)]. The length and width of the line were taken from the physical dimensions of the inductor and the resistivity ( $3.5 \times 10^{-6} \Omega\text{-cm}$ ) was found from dc resistance measurements. In addition to resistance, the microstrip line model accounts for distributed capacitance of the line to the backside of the wafer. The microstrip line also has a distributed self-inductance. Since the total inductance of the spiral is the sum of the self and mutual inductances [7], to represent the overall inductance of the spiral a mutual inductance ( $L_m$ ) was added in series with the microstrip line. Finally, a capacitance ( $C$ ) in parallel was added to account for capacitance between the windings. A typical fit of modeled to measured inductance and quality factor for both SOS and Si inductors is shown in Fig. 2.

Small signal model parameters, self-resonant frequency, and quality factor for the five- and eight-turn inductors are shown in Table I. We can see from Table I that the parameter  $L_m$  does not change for the inductors on different substrates. Over the frequency range studied, the inductance ( $L$ ) is only a function of the number of turns, inner and outer radii of the spiral, and the width and spacing of the conductors [8], [9]. The winding capacitance ( $C$ ) is primarily dependent on the spacing of the conductors. Note that the substrate capacitance  $C_s$  and substrate resistance  $R_s$  are needed to accurately model the inductors on bulk silicon, but are not necessary for the SOS inductors. The substrate parameters  $C_s$  and  $R_s$  represent the capacitance across the 1.7- $\mu\text{m}$ -thick insulating oxide and resistance associated with the conductive silicon substrate. As expected,  $C_s$  increases and  $R_s$  decreases as the inductor area increases.

#### V. CONCLUSION

We have shown that with no additional or novel processing steps, SOS technology can provide inductors with high self-resonant frequencies and good quality factors. The inductors are significantly better than those fabricated on bulk silicon. By combining the inductors with high-performance MOSFET's

TABLE I

SMALL SIGNAL MODEL PARAMETERS AND FIGURES OF MERIT FOR FIVE- AND EIGHT-TURN INDUCTORS ON SOS AND Si

| Substrate | Turns | $L_{tot}$ (nH) | $f_{sr}$ (GHz) | $Q_{peak}$ | Length (μm) | $L_m$ (nH) | C (fF) | $C_s$ (fF) | $R_s$ (Ω) |

|-----------|-------|----------------|----------------|------------|-------------|------------|--------|------------|-----------|

| Sapphire  | 5     | 4.0            | 13.9           | 11.9       | 2200        | 1.3        | 35     | -          | -         |

| Sapphire  | 8     | 10.7           | 7.0            | 9.9        | 4273        | 5.4        | 50     | -          | -         |

| Si        | 5     | 4.0            | 9.2            | 3.6        | 2200        | 1.3        | 35     | 150        | 320       |

| Si        | 8     | 10.7           | 3.4            | 3.0        | 4273        | 5.4        | 50     | 210        | 200       |

[1], [2], silicon-on-sapphire technology appears well suited for circuits operating in the microwave regime.

#### REFERENCES

- [1] C. E. Chang *et al.*, "Microwave characterization of sub-micron n- and p-channel MOSFET's fabricated with thin film silicon-on-sapphire," in *MTT-S Dig.*, 1994, pp. 405-408.

- [2] P. R. de la Houssaye *et al.*, "Microwave performance of optically fabricated T-gate thin film silicon-on-sapphire based MOSFET's," *IEEE Electron Device Lett.*, vol. 16, no. 6, p. 289, June 1995.

- [3] J. Y.-C. Chang *et al.*, "Large suspended inductors on silicon and their use in a 2-μm CMOS RF amplifier," *IEEE Electron Device Lett.*, vol. 14, no. 5, pp. 246-248, May 1993.

- [4] C.-Y. Chi and G. M. Rebeiz, "Planar millimeter-wave microstrip lumped elements using micro-machining techniques," in *IEEE MTT-S Dig.*, 1994, pp. 657-660.

- [5] D. Lovelace *et al.*, "Silicon MMIC inductor modeling for high volume, low cost applications," *Microwave J.*, Aug. 1994, p. 60.

- [6] K. B. Ashby *et al.*, "High  $Q$  inductors for wireless applications in a complementary silicon bipolar process," in '94 *Bipolar/BiCMOS Circuits Tech. Mtg.*, pp. 179-182.

- [7] H. M. Greenhouse, "Design of planar rectangular microelectronic inductors," *IEEE Trans. Parts, Hybrids Packag.*, vol. PHP-10, no. 2, pp. 101-109, June 1974.

- [8] F. S. Burkett, Jr., "Improved design for thin film inductors," in *Proc. '71 Electron. Comp. Conf.*, Washington, DC, 1971, pp. 183-193.

- [9] H. A. Wheeler, "Simple inductance formulas for radio coils," in *Proc. Inst. Radio Eng.*, XVI, Oct. 1928, pp. 1398-1400.